スマートフォンの実現に欠かせない低電力LSIテスト技術とは

半導体メーカーの経営も左右するLSIテスト技術

スマートフォンやパソコンなどの電子製品の心臓部に当たるLSI(大規模集積回路) は製造後、良品と不良品に振り分けるためのテストが必要です。具体的には、LSI設計データからテスト入力(試験問題相当)と期待応答(標準回答相当)を作成し、LSIをテスターにかけて出てきた実応答と比較してLSIの良否判定を行うのです。しかし、テスト入力がよくなければ、不良品を良品として出荷したり良品を不良品として破棄したりすることになり、市場の信頼性や価格競争力を失います。そのため、LSIテスト技術の良し悪しは半導体メーカーの経営も左右すると言っても過言ではありません。

LSIの低消費電力化は世界的なトレンド

最近のLSIは、ひとつのチップに数億個の素子が入っており、また配線幅も髪の毛の数千分の1という微細加工がされているため、そのテストが極めて難しいのです。さらにLSIの世界的なトレンドとして、スマートフォン向けなどに需要が急増しているのが低消費電力LSIです。しかし、低消費電力LSIのテストでは、実際の使用時よりはるかに高いテスト電力が発生してしまうため、テスト中のLSIの誤動作や熱破壊といった深刻な問題に直面しています。

低消費電力LSIテスト技術

そこで、低消費電力テスト技術が強く求められています。特に、LSI回路内の異常に高いテスト電力を有する危険部位を電力解析によって精確に特定し、その部分の論理状態変化量をテスト入力データや回路設計の変更によって効果的に削減するというPLPT(Pinpoint Low-Power Test)技術の確立に向かって、半導体メーカー、設計自動化システムメーカー、大学や研究機関を巻き込んだ熾烈な研究競争が世界で始まっています。低消費電力テスト技術を制することは、スマートフォンに代表されるモバイル電子機器の開発競争を制することになるでしょう。

※夢ナビ講義は各講師の見解にもとづく講義内容としてご理解ください。

※夢ナビ講義の内容に関するお問い合わせには対応しておりません。

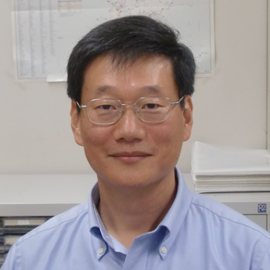

先生情報 / 大学情報

![選択:[SDGsアイコン目標9]](https://telemail.jp/shingaku/requestren/img/data/SDGs-9-active.png )